On some newer platforms of intel (confirmed on nehalem, sandy/ivy bridge), coreboot after commit [2ac149d294af795710eb4bb20f093e9920604abd](https://review.coreboot.org/cgit/coreboot.git/commit/?id=2ac149d294af795710eb4bb20f093e9920604abd) registers an SMI to lockdown some registers on the chipset, as well as access to the SPI flash, optionally. The SMI will always be triggered by coreboot during S3 resume, but can be triggered by either coreboot or the payload during normal boot path. Enabling lockdown access to SPI flash will effectly write-protect it, but there is no runtime option for coreboot to control it, so letting coreboot to trigger such SMI will leave the owner of the machine lost any possibility to program the SPI flash with its own OS, and becomes a nightmare if the machine is uneasy to disassemble, so a scheme could be implement, in which the SMI to lockdown chipset and SPI flash is left for a payload to trigger, and temporarily disabling such triggering in order to program the SPI flash needs authentication. I have implemented a passcode-protected runtime-disableable lockdown with grub, described [here](https://github.com/hardenedlinux/Debian-GNU-Linux-Profiles/blob/master/docs/hardened_boot/grub-for-coreboot.md#update-for-coreboot-after-commit-2ac149d294af795710eb4bb20f093e9920604abd). In order to implement a similar scheme for Heads, I wrote [io386](https://github.com/hardenedlinux/io386). With this commit, io386 will be called before entering boot routine to trigger the SMI to finalize the chipset and write protect the SPI flash at the same time. Entering recovery shell will leave the flash writable. (The authentication routine implemented in previous revisions has been split as an independent commit.) Originally proposed under PR#326

Heads: the other side of TAILS

Heads is a configuration for laptops and servers that tries to bring more security to commodity hardware. Among its goals are:

- Use free software on the boot path

- Move the root of trust into hardware (or at least the ROM bootblock)

- Measure and attest to the state of the firmware

- Measure and verify all filesystems

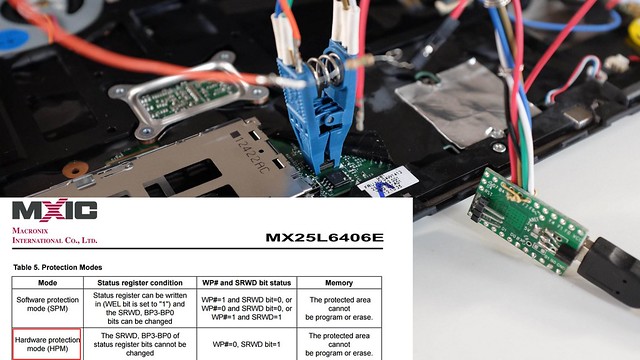

NOTE: It is a work in progress and not yet ready for non-technical users. If you're interested in contributing, please get in touch. Installation requires disassembly of your laptop or server, external SPI flash programmers, possible risk of destruction and significant frustration.

More information is available in the 33C3 presentation of building "Slightly more secure systems".

Documentation

Please refer to Heads-wiki for your Heads' documentation needs.

Building heads

make BOARD=board_name where board_name is the name of the board directory under ./boards directory.

In order to build reproducible firmware images, Heads builds a specific

version of gcc and uses it to compile the Linux kernel and various tools

that go into the initrd. Unfortunately this means the first step is a

little slow since it will clone the musl-cross-make tree and build gcc...

Once that is done, the top level Makefile will handle most of the

remaining details -- it downloads the various packages, verifies the

hashes, applies Heads specific patches, configures and builds them

with the cross compiler, and then copies the necessary parts into

the initrd directory.

There are still dependencies on the build system's coreutils in

/bin and /usr/bin/, but any problems should be detectable if you

end up with a different hash than the official builds.

The various components that are downloaded are in the ./modules

directory and include:

We also recommend installing Qubes OS,

although there Heads can kexec into any Linux or

multiboot

kernel.

Notes:

- Building coreboot's cross compilers can take a while. Luckily this is only done once.

- Builds are finally reproducible! The reproduciblebuilds tag tracks any regressions.

- Currently only tested in QEMU, the Thinkpad x230, Librem series and the Chell Chromebook. ** Xen does not work in QEMU. Signing, HOTP, and TOTP do work; see below.

- Building for the Lenovo X220 requires binary blobs to be placed in the blobs/x220/ folder. See the readme.md file in that folder

- Building for the Librem 13 v2/v3 or Librem 15 v3/v4 requires binary blobs to be placed in the blobs/librem_skl folder. See the readme.md file in that folder

QEMU:

OS booting can be tested in QEMU using a software TPM. HOTP can be tested by forwarding a USB token from the host to the guest.

For more information and setup instructions, refer to the qemu-coreboot-fbwhiptail-tpm1-hotp documentation.

coreboot console messages

The coreboot console messages are stored in the CBMEM region

and can be read by the Linux payload with the cbmem --console | less

command. There is lots of interesting data about the state of the

system.